Practical Guide to Semiconductor Wafer Dicing: Materials, Blades, and Process Optimization

-

Posted by

contactor6

Table of Contents

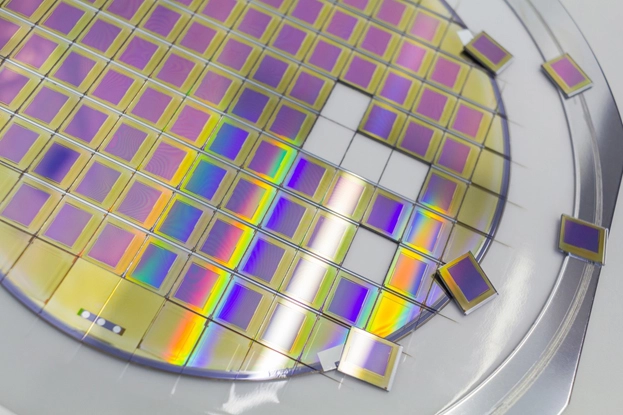

ToggleSemiconductor wafers are the foundation of nearly all modern electronics, from integrated circuits and photonic devices to advanced power components. As device geometries shrink and packaging density increases, the requirements placed on wafer dicing processes have become more demanding. The goal is no longer just separating dies but doing so with maximum yield, minimal chipping, and precise kerf control.

Dicing semiconductor wafers is a complex balance of material properties, blade technology, and process parameters. Materials such as silicon, gallium arsenide (GaAs), lithium niobate (LiNbO₃), indium phosphide (InP), and silicon carbide (SiC) each present unique challenges due to differences in hardness, brittleness, and thermal behavior. Blade selection, feed rate, spindle speed, mounting methods, and coolant delivery must be carefully optimized for each substrate to achieve consistent and reliable results.

This article provides a practical guide to semiconductor wafer dicing. It covers the characteristics of the most common wafer materials, recommended blade types, critical process parameters, and common challenges such as chipping, heat buildup, and kerf width control. The goal is to equip engineers and process technicians with the knowledge needed to make informed decisions, improve wafer yields, and extend blade life in demanding production environments.

Common Materials: Silicon (Si), LiNbO₃ (Lithium Niobate), GaAs (Gallium Arsenide), InP (Indium Phosphide), and SiC (Silicon Carbide). Each material presents unique properties that determine its application, dicing challenges, and blade requirements.

Silicon (Si)

Silicon is the most widely used semiconductor material, accounting for the majority of integrated circuits, MEMS devices, and power components. It offers high purity, excellent crystalline structure, and mature manufacturing processes. Wafer diameters up to 12″ (300 mm) are standard in advanced fabs. Dicing silicon is generally straightforward, but precision is critical to minimize backside chipping and subsurface damage, especially in thin wafers below 100 µm. Finer diamond grit sizes and optimized coolant delivery are recommended for high-yield IC production.

Lithium Niobate (LiNbO₃)

Lithium niobate is primarily used for photonic, optical, and RF applications, including waveguides, modulators, and surface acoustic wave (SAW) devices. It is relatively brittle and prone to subsurface microcracking if cutting parameters are not optimized. Dicing requires softer bond blades and fine diamond grit sizes to protect delicate structures. Coolant management is especially important, as inadequate flushing can increase edge chipping. Because wafers are often thin (sub-200 µm), proper mounting with UV-release tape or dual-layer systems is critical.

Gallium Arsenide (GaAs)

GaAs is used in high-frequency, optoelectronic, and power devices, such as LEDs, laser diodes, and RF amplifiers. It offers superior electron mobility compared to silicon but is much more brittle. GaAs wafers are highly sensitive to microcracks and thermal stress. Cutting must be performed at lower feed rates and higher spindle speeds with blades that minimize cutting force. Nickel bond or hybrid bond blades with fine diamonds are generally preferred. Because GaAs is toxic in dust form, effective coolant flow and slurry management are critical for both operator safety and die yield.

Indium Phosphide (InP)

InP is common in optoelectronics, photonic integrated circuits, and high-speed communication devices. It provides excellent electron velocity and direct bandgap properties. However, InP is soft and brittle, making it difficult to dice cleanly. Feed rates must be carefully reduced to avoid edge cracking, and blade selection must prioritize edge smoothness over cutting speed. UV-release tape is often required for thin wafers, and coolant additives may be introduced to improve cut stability and reduce blade loading.

Silicon Carbide (SiC)

SiC is one of the hardest semiconductor materials and is increasingly used in power electronics, EV components, and high-temperature devices due to its wide bandgap and thermal stability. Its hardness presents significant challenges in dicing: blade wear is accelerated, cutting forces are higher, and heat buildup can quickly damage wafers. Stronger bond blades with larger diamond grit sizes are often required, but they must still balance chipping control. High spindle torque, optimized coolant delivery (sometimes high-pressure systems), and careful mounting are critical to achieve reliable results.

General Observations Across Materials

- As wafers become thinner (below 100 µm), regardless of material, mounting and handling become as important as the cutting process itself.

- Brittle substrates like LiNbO₃, GaAs, and InP require fine diamonds, softer bonds, and lower feed rates to minimize cracking.

- Hard materials like SiC demand more aggressive parameters but require advanced coolant systems and frequent blade monitoring.

- The choice of blade bond (Nickel, Hybrid, or Resin) and diamond grit size is always dictated by material hardness, thickness, and desired die quality.

Semiconductor wafer materials, including their properties, applications, dicing challenges, and recommended blade choices:

|

Material |

Key Properties |

Primary Applications |

Dicing Challenges |

Recommended Blade & Setup |

|---|---|---|---|---|

|

Silicon (Si) |

High purity, excellent crystalline structure, mature manufacturing process | Integrated circuits (ICs), MEMS, sensors, power electronics |

Relatively easy to dice, but thin wafers (<100 µm) prone to backside chipping and warpage |

SMART CUT® Nickel Bond or HYBRID Series; diamond size 4–6 µm; feed rate 40–75 mm/s; spindle speed 30–40 krpm; DI water coolant |

|

Lithium Niobate (LiNbO₃) |

Brittle, prone to subsurface cracks; sensitive to coolant flow and mounting stress |

RF filters, photonics, waveguides, SAW devices |

lastics, composites, ceramics, delicate parts where liquid may cause cracking or contamination |

HYBRID bond with fine grit (3–4 µm); slower feed rate (15–30 mm/s); spindle speed 35–45 krpm; UV-release tape mounting; DI water with surfactants |

|

Gallium Arsenide (GaAs) |

High electron mobility, direct bandgap |

LEDs, laser diodes, RF amplifiers, solar cells |

Very brittle, microcracks form easily; toxic dust requires strict slurry control |

Nickel Bond blades, fine grit (4 µm); low feed rate (10–25 mm/s); spindle speed 40–50 krpm; strong coolant flushing with DI water |

|

Indium Phosphide (InP) |

High electron velocity, direct bandgap, brittle | Photonic ICs, lasers, high-speed communications |

Soft and brittle; prone to edge cracking and blade loading |

HYBRID or soft bond, fine grit (2–4 µm); low feed rate (10–20 mm/s); spindle speed 35–45 krpm; UV-release tape; DI water with lubricants |

|

Silicon Carbide (SiC) |

Extremely hard, wide bandgap, thermally stable | Power electronics, EV inverters, high-temp devices |

Very hard to cut, rapid blade wear, high heat generation |

Nickel Bond with larger grit (6–8 µm); moderate feed rate (20–40 mm/s); spindle speed 25–35 krpm; high-pressure DI water coolant; strong spindle torque |

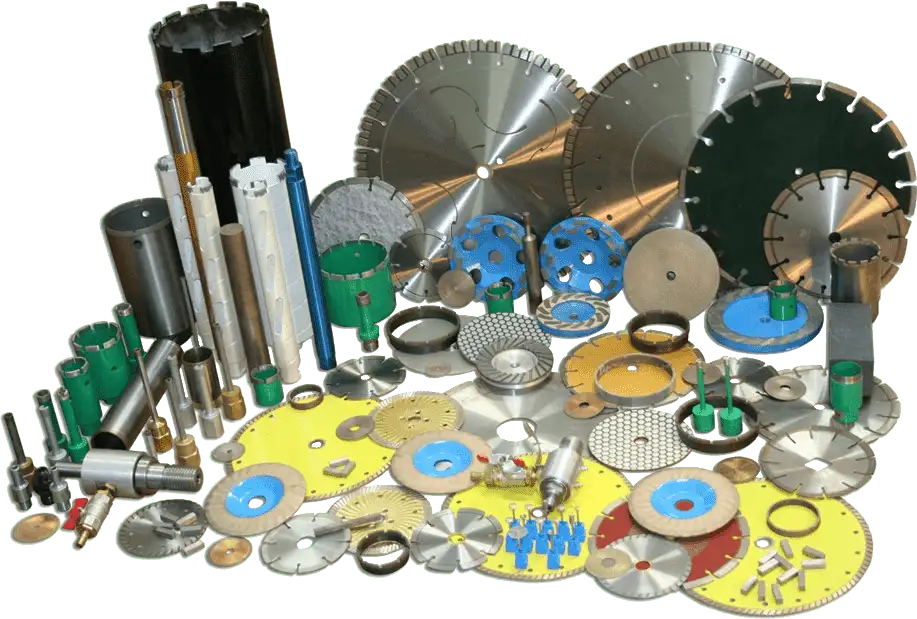

Dicing Blade Recommendations

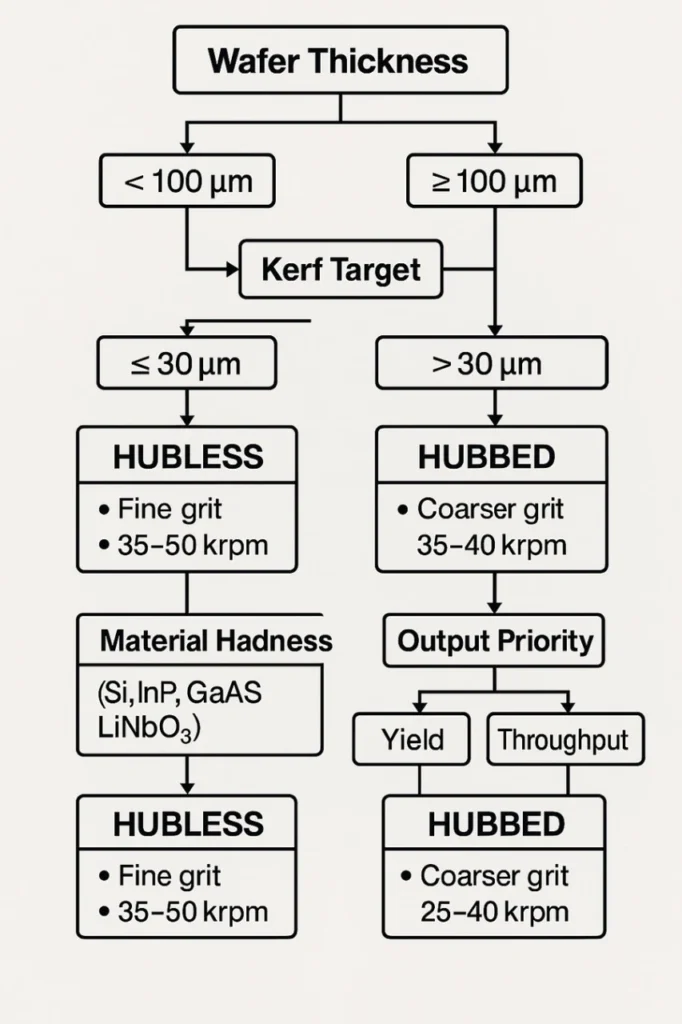

In semiconductor wafer dicing, the choice between hubless and hubbed blades depends on wafer thickness, kerf requirements, and desired output.

Hubless blades are widely used for thin and ultra-thin wafers, especially when kerf widths must be extremely narrow in the 12 to 25 micron range. They provide flexibility, allow the thinnest blade designs, and are stabilized with flanges to control side runout. They are preferred when maximum die strength, tight kerf control, and process flexibility are the main priorities. Hubbed blades, by contrast, bond directly to a precision hub, which improves stability, reduces vibration, and makes blade replacement faster. They are best for thicker wafers, kerf widths above 30 microns, and high-throughput production where consistency and repeatability are critical.

For wafers below 100 microns with kerfs of 12 to 25 microns, hubless blades with fine diamond grit (2–4 µm) provide the lowest cutting forces and best edge quality, particularly for brittle materials such as GaAs, InP, and LiNbO₃. For wafers between 100 and 200 microns with kerfs of 20 to 30 microns, hubless blades remain the preferred choice due to their low-force cutting and precision. Once wafers reach 200 to 500 microns and kerfs of 30 to 50 microns, hubbed blades often become the better option because they provide the stability needed at higher spindle speeds and faster feed rates. For wafers above 500 microns or with kerfs wider than 40 microns, hubbed blades are strongly recommended, since they handle greater cutting forces, provide longer life, and perform well in heavy-duty applications such as SiC.

When maximum die strength is required, hubless blades with very fine grit and softer bonds are best suited, especially for thin and brittle wafers. When throughput is the priority, hubbed blades with nickel bonds and slightly coarser grits (4–6 µm or even 6–8 µm for SiC) provide stability and durability. If the goal is lowest cost per die, hubless blades often give the advantage by enabling smaller kerfs and higher die count, though in cases where blade wear dominates costs, hubbed blades may reduce tool changes and dressing frequency. In environments where frequent process changes are needed across multiple wafer types, hubless blades are more flexible, while in fixed, high-volume production, hubbed blades are more efficient and consistent.

Material also influences the choice. Silicon wafers under 150 microns typically use hubless blades, while standard-thickness silicon wafers over 200 microns often shift toward hubbed. GaAs, InP, and LiNbO₃ are brittle and generally cut with hubless blades at lower feed rates and higher RPMs using fine grit. Thicker versions of these wafers may sometimes justify hubbed blades if throughput is more important than maximum edge quality. SiC, due to its extreme hardness, is best cut with hubbed blades when thickness is over 200 microns or kerfs exceed 30 microns, though hubless blades can be applied on thinner SiC wafers if exposure is short, flanges are large, and coolant delivery is optimized.

Across all materials, flange diameter, exposure ratio, spindle runout, and coolant flow are decisive. Large flanges, short blade exposures, and properly applied torque reduce side runout in hubless systems, while hubbed blades inherently reduce sensitivity to mounting errors. Dressing must be scheduled based on cut length to keep blades sharp, and coolant delivery, whether standard DI water, surfactant-enhanced, or high-pressure systems—is critical to prevent heat buildup, chipping, and blade loading. In practice, hubless blades dominate in research, prototyping, and advanced packaging where flexibility and fine kerf control matter most, while hubbed blades are preferred in high-volume semiconductor production where stability, repeatability, and throughput are the main drivers.

SMART CUT® Nickel Bond or HYBRID Series

These blade types are widely preferred for semiconductor wafer dicing because they provide an optimal balance between aggressiveness and precision. Nickel bond dicing blades hold diamond particles firmly, allowing them to cut brittle materials like silicon, GaAs, and LiNbO₃ with minimal pull-out or subsurface damage. They are also durable and resist premature wear, making them suitable for medium to high-volume production. HYBRID series dicing blades combine characteristics of resin and metal bonds, offering smoother cut surfaces, reduced chipping, and consistent performance across different wafer materials. This versatility makes them ideal for facilities processing multiple substrate types on the same line. Selection between Nickel Bond and HYBRID depends on the material hardness, desired die edge quality, and throughput requirements.

Diamond Size: 4 – 6 microns

Diamond grit size directly affects both cut quality and processing speed. A smaller diamond size (2–4 µm) provides smoother surfaces and reduced microcracking but cuts slower and may wear more quickly. A larger diamond size (6–8 µm) increases cutting speed and blade life but can leave a rougher edge and higher chip levels. The 4–6 µm range is widely used in semiconductor dicing because it balances surface finish, die strength, and throughput. For ultra-thin wafers or high-value devices, manufacturers often lean toward the finer end of this range to protect fragile structures.

Blade Thickness: 0.0008” – 0.0016” (20–40 µm)

Blade thickness determines kerf width, material loss, and die density. Thinner blades (around 20 µm) are critical for advanced packaging where scribe streets are narrow and maximum die count per wafer is required. However, ultra-thin blades are more fragile, demand precise spindle alignment, and are sensitive to vibration or improper mounting. Thicker blades (up to 40 µm) provide greater stability, longer life, and better tolerance to cutting force variations, but they consume more material and reduce the number of usable dies. Maintaining tight kerf control is especially important in high-density designs where even a 1–2 µm deviation in width can significantly affect yield and downstream assembly. For this reason, precision flanges, controlled torque during mounting, and advanced coolant delivery systems are used to stabilize the blade and minimize side runout.

Dicing Process Recommendations

Feed Rate: 25 – 75 mm/sec

Feed rate is one of the most sensitive parameters in wafer dicing. If the feed rate is too high, cutting forces increase, which leads to front-side and backside chipping, blade deflection, and premature wear. If the feed rate is too low, throughput suffers and the blade can load up with debris, generating more heat and reducing blade life. Softer wafers such as GaAs, InP, or LiNbO₃ must be diced at slower feed rates (10–30 mm/sec) to minimize cracking, while harder and stronger wafers such as silicon can handle faster feed rates (40–75 mm/sec). Optimizing feed rate always requires balancing productivity with die quality and blade cost.

Spindle Speed: 30,000 – 50,000 RPM

Higher spindle speeds distribute the cutting force across more diamond particles, reducing stress on each grain and improving cut smoothness. This helps maintain edge quality, especially in ultra-thin wafers and brittle compound semiconductors. However, extremely high spindle speeds require a rigid spindle, precision-balanced flanges, and excellent coolant delivery to avoid vibration and heat buildup. Blade diameter also directly dictates allowable spindle speeds: smaller diameter blades can run at higher RPMs, while larger blades require lower RPMs to stay within safe surface speed limits.

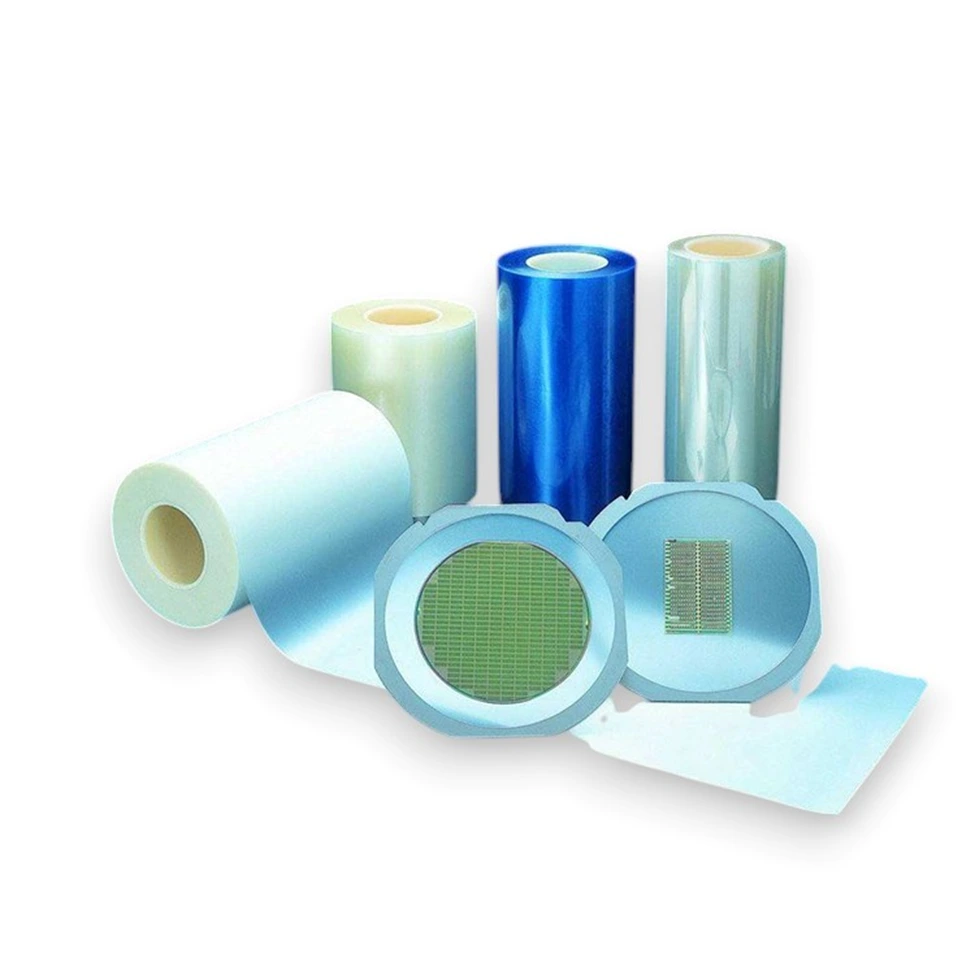

Mounting: Blue or UV-release dicing tape

Proper mounting is critical to avoid wafer breakage and uneven cut depths. Blue tape is common for standard silicon wafers due to its stable adhesion and low cost. UV-release tape is widely used for thin wafers because the adhesive weakens after UV exposure, allowing dies to be easily removed without mechanical stress.

For extremely thin wafers (<100 µm), dual-layer mounting systems are sometimes used: one layer provides adhesion to hold the wafer during dicing, and the second layer absorbs stress to prevent flexing or cracking. Vacuum chuck stability, tape flatness, and controlled tension during mounting all influence dicing precision.

Cooling: DI water with additives

Deionized water is the industry standard coolant because it prevents ionic contamination and supports high flushing efficiency. However, in high-precision or difficult-to-dice wafers, additives such as surfactants, lubricants, or antistatic agents may be introduced. Such as SMART CUT Dicing Coolant. These additives reduce friction, improve debris removal, and help maintain a consistent temperature at the cut zone. In some advanced setups, carbon dioxide is bubbled into DI water to lower surface tension, reduce static buildup, and enhance cooling. High-pressure or multi-jet coolant systems are preferred for narrow kerfs, since they can penetrate the cutting channel more effectively and prevent slurry packing.

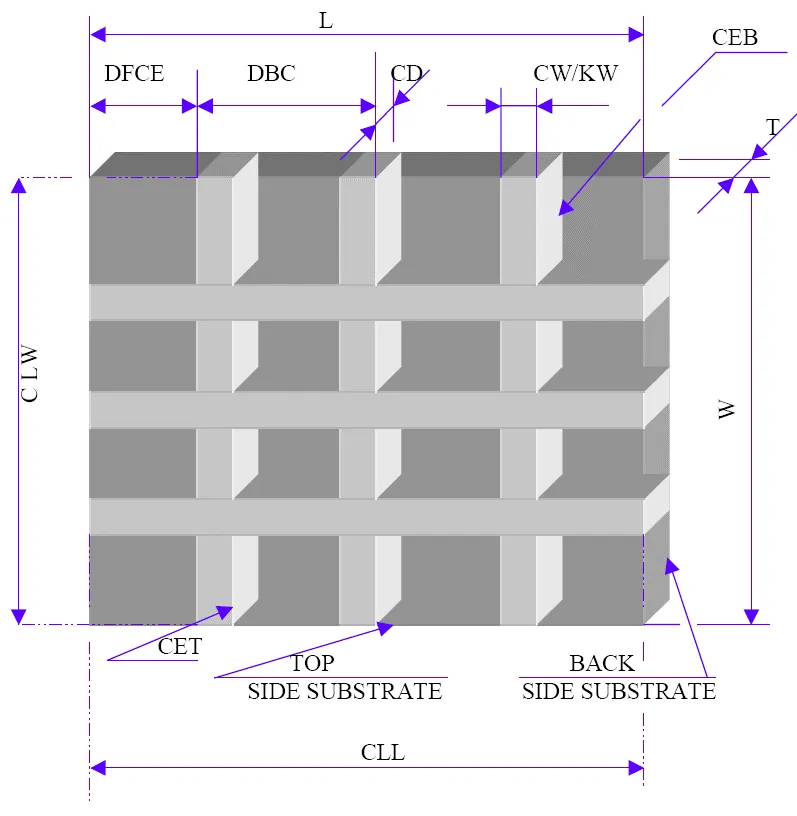

Wafer Specifications

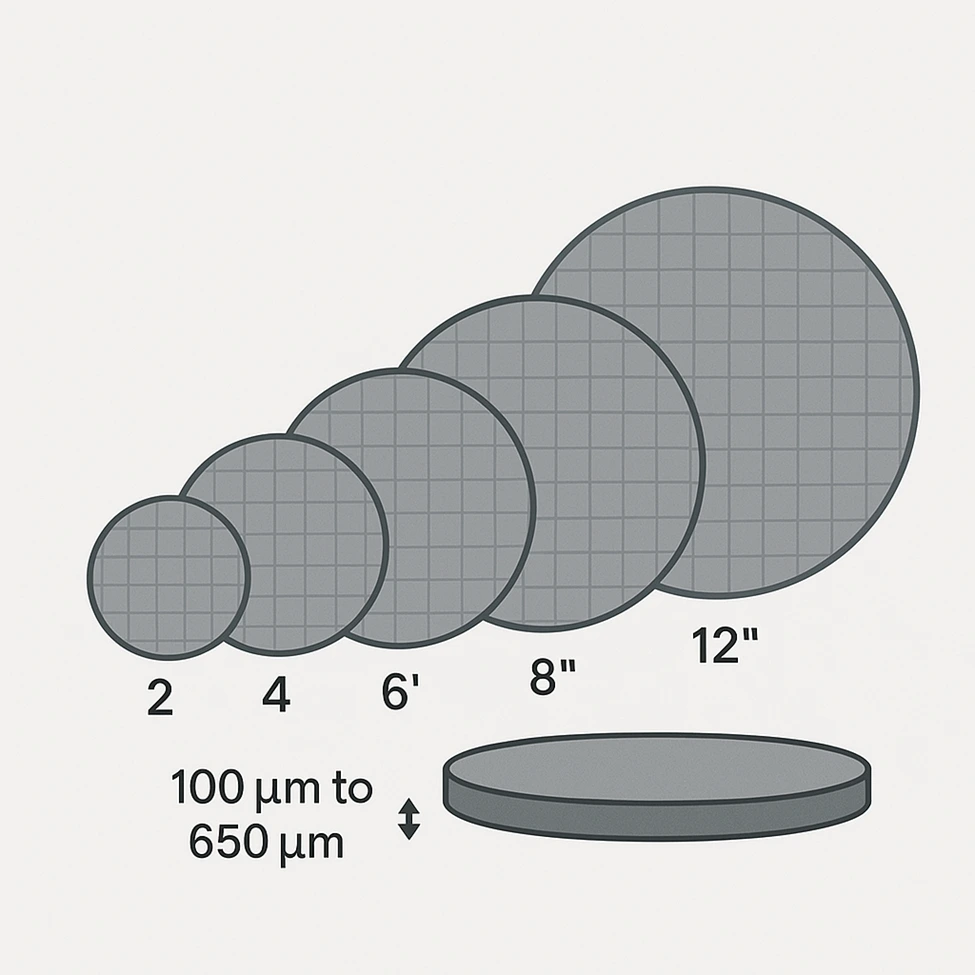

Diameter

Semiconductor wafers are manufactured in standard diameters of 2”, 3”, 4”, 6”, 8”, 12”, and experimental 18”. Research and prototyping often use 2” and 4” wafers due to lower cost and material availability. Industrial production lines predominantly use 6” and 8” wafers, while 12” (300 mm) wafers dominate high-volume manufacturing in advanced semiconductor fabs. Larger diameters allow more dies per wafer, reducing cost per chip, but they require more advanced equipment, tighter flatness control, and greater process stability.

Thickness

Wafer thickness typically ranges from 100 µm to 650 µm depending on diameter and application. Larger wafers require greater thickness for mechanical stability during handling, while advanced packaging and flexible electronics may reduce wafers to below 50 µm using back-grinding and chemical-mechanical polishing (CMP). Ultra-thin wafers are critical for 3D packaging, MEMS devices, and stacked die configurations, but they are highly prone to breakage during dicing and handling. Specialized mounting tapes and dual-layer supports are often required to process wafers below 75 µm.

Flatness and Warp Control

Flatness and warp directly influence cut depth uniformity, blade stability, and die yield. Even small warpage—on the order of a few microns—can cause uneven kerf depths, backside chipping, or blade breakage. Warp issues are more common in compound semiconductors like GaAs, InP, and SiC, where crystal growth methods introduce stress. For ultra-thin wafers, stress relief steps and careful thermal processing are required to minimize bowing. Dicing equipment must include precision vacuum chucks, tape tension controls, and real-time depth monitoring to compensate for wafer warp.

Edge Exclusion and Scribe Lines

Wafers are not fully usable to the very edge. Edge exclusion zones (typically 1–3 mm from the wafer edge) are defined to avoid defects caused by beveling and handling. Scribe lines or streets, usually 50–100 µm wide, are the designated cutting paths between dies. As device density increases, narrower scribe lines are required, which demand thinner blades, tighter runout tolerances, and improved kerf control.

Surface Quality

Wafer surfaces must meet strict specifications for roughness and defect density. Back-grinded or polished wafers require controlled surface roughness to maintain adhesion to mounting tape while preventing stress concentration points. Poor surface quality leads to higher breakage rates during dicing and reduced device reliability.

Typical Concerns

Feed Rates

Initial test cuts often require low feed rates between 1 mm/s and 5 mm/s. This helps evaluate how the wafer responds to the cutting conditions, especially when working with brittle materials like GaAs or LiNbO3. For full production, feed rates are usually increased to 25 – 75 mm/s depending on wafer thickness, diamond grit size, and blade bond type. Going too fast risks excessive chipping and wafer breakage, while going too slow can reduce throughput and cause unnecessary blade wear due to prolonged contact.

Spindle Speeds (RPMs)

General dicing is performed at 15,000 to 30,000 RPM. Advanced operations use 30,000 to 50,000 RPM to improve precision. Higher spindle speeds reduce cutting forces per diamond particle, which lowers the chance of large edge chipping and minimizes microcracks. However, extremely high RPMs require stable mounting, balanced flanges, and effective coolant delivery to prevent spindle runout, vibration, or thermal stress. Selecting the correct RPM is always tied to blade diameter, exposure, and wafer thickness.

Mounting Type

Secure wafer mounting is critical because even minor movement can lead to misalignment and breakage. Vacuum chucks are the standard for most semiconductor wafers, especially thin wafers under 200 µm, since they hold without mechanical pressure. Magnetic chucks are sometimes used for specific substrates or experimental processes. For dicing tape, blue tape provides reliable adhesion, UV-release tape is preferred for easy post-dicing separation, and thermal release tape is used for very thin wafers to reduce stress during die removal. Mounting conditions must also account for wafer bow or warp, which can affect cut depth uniformity.

Coolants

Deionized (DI) water is the standard coolant due to its purity and compatibility with semiconductor materials. Proper cooling prevents thermal cracking, helps flush debris from the kerf, and extends blade life. Additives such as SMART CUT lubricants or surfactants can reduce friction and improve debris removal, leading to smoother cuts. In sensitive environments, CO₂ bubblers are sometimes introduced into the DI water line. This slightly acidifies the water, helping control pH, suppress static charge, and improve cooling performance. The choice of coolant delivery method flood, jet, or high-pressure also affects both wafer quality and blade wear.

Chipping in Silicon Wafer Dicing

Chipping is one of the most significant challenges when dicing silicon wafers because it directly affects die strength, electrical performance, and overall yield. Silicon is less brittle than materials like GaAs or LiNbO₃, but as wafer thicknesses decrease to below 150 µm, the risk of both front-side and backside chipping rises dramatically. Backside chipping is particularly damaging in silicon because it often extends into active device layers, producing microcracks that may not be visible under optical inspection but can propagate during thermal cycling or packaging steps, leading to latent reliability failures.

Several process parameters directly influence chipping in silicon wafer dicing. Feed rate plays a critical role: excessive feed rates increase cutting forces, which cause larger chip sizes and edge damage, while feed rates that are too low can cause blade loading and thermal stress, which also induce microcracks. Spindle speed must be matched to the blade diameter and kerf requirement; operating at 30,000–40,000 RPM for hubbed blades or up to 50,000 RPM for hubless blades spreads the cutting load across more diamond particles, reducing localized stress and chipping. Blade bond hardness also affects chip formation. A softer bond releases worn diamond particles more quickly, exposing fresh sharp diamonds that cut with less force and minimize chip size, while a harder bond may extend blade life but increases the risk of larger chips if the blade dulls.

Coolant delivery is another critical factor. Silicon wafers generate fine abrasive debris that can clog the kerf if not flushed properly. Insufficient coolant flow allows debris to recirculate, increasing mechanical stress at the cutting edge and causing larger backside chips. Using deionized water with surfactant additives reduces surface tension, improves debris removal, and lowers blade-to-wafer friction. High-pressure multi-jet coolant systems are particularly effective when cutting ultra-thin silicon wafers, as they ensure coolant penetration deep into the kerf and maintain temperature stability at the blade–wafer interface.

Wafer mounting quality also strongly influences chipping. Uneven tape tension, poor vacuum distribution, or trapped air pockets can cause local wafer flexing during dicing. This flexing changes the effective cut depth, increasing backside breakout and chip size. For thin silicon wafers (<100 µm), UV-release tapes or dual-layer tapes are often used to provide additional support and reduce mechanical stress during cutting.

From a yield perspective, even small chips can be unacceptable in high-density silicon devices. In advanced logic or memory wafers, chip sizes greater than 5–10 µm may disqualify dies. As device geometries continue to shrink, tolerances for chipping are even tighter, often requiring advanced HYBRID or fine-grit hubless blades with thicknesses as low as 20 µm to maintain kerf precision.

Process optimization for silicon wafer dicing therefore requires balancing feed rate, spindle speed, bond hardness, coolant delivery, and mounting method to minimize both front-side and backside chipping. Continuous monitoring of blade wear and spindle runout, combined with in-line die strength testing, is essential for ensuring that chipping remains within acceptable limits across high-volume production.

Blade Wear in Silicon Wafer Dicing

Blade wear is a major factor influencing both cut quality and overall cost in silicon wafer dicing. As the dicing blade is used, diamond particles become worn down or dislodged, reducing their cutting efficiency. The bond matrix that holds the diamonds also gradually smooths, leaving fewer sharp points in contact with the wafer. This reduction in effective diamond exposure increases cutting resistance, forcing the operator or equipment to apply more pressure to maintain throughput.

In silicon, this additional force causes several problems. Increased pressure accelerates subsurface damage, where microcracks extend below the wafer surface into functional device layers. Even if these cracks are invisible during inspection, they may propagate during downstream steps such as die attach, wire bonding, or thermal cycling, ultimately causing early device failures. Blade wear also results in kerf widening, as the blade deflects under higher loads or as sidewall friction increases. When kerf deviates by even 1–2 µm from specification, die alignment in packaging can be compromised, leading to reduced yield.

Managing blade wear requires both preventive dressing and process monitoring. Dressing is used to strip away dull bond material and expose fresh diamonds, restoring sharp cutting edges. However, every dressing cycle slightly reduces blade diameter and thickness, limiting the total usable life of the blade. For silicon wafers, dressing frequency is determined by a combination of wafer thickness, feed rate, and grit size. Ultra-thin silicon wafers diced with fine-grit blades (2–4 µm) may require more frequent dressing to maintain cut quality, while standard-thickness wafers diced with 4–6 µm grit blades can often go longer between dressing cycles.

Advanced blade bonds improve wear resistance in silicon applications. Nickel bond blades provide strong retention of diamond particles, delivering longer life and stable kerf control. Hybrid bonds combine the cutting aggressiveness of resin bonds with the durability of metal bonds, making them particularly effective in applications where a balance between cut quality and longevity is required. While resin bond blades can produce smoother edges, they wear more quickly and require close monitoring, especially in high-throughput production.

Predictive maintenance practices are essential to control wear in silicon wafer dicing. Many fabs monitor cut length per blade, number of wafers processed, or spindle load trends to determine when a blade is nearing the end of its effective life. Automated dicing saws often integrate spindle power monitoring to detect increased load, which indicates dulling diamonds or excessive friction. By replacing blades before catastrophic wear occurs, manufacturers avoid sudden kerf deviations, excessive chipping, or wafer breakage, while also minimizing downtime.

In advanced silicon wafer dicing, where kerfs may be as narrow as 20–30 µm and wafers are frequently thinned below 100 µm, controlling blade wear is directly tied to yield and die strength. A poorly maintained or worn blade can instantly damage hundreds of dies in a single wafer. For this reason, blade wear management is treated as a critical process parameter, on par with feed rate, spindle speed, and coolant flow.

Heat Buildup in Silicon Wafer Dicing

Heat management is one of the most critical aspects of successful wafer dicing. Excessive temperature rise during cutting affects both the wafer and the dicing blade. On the wafer side, localized heating creates thermal expansion mismatch between the substrate and the mounting tape, leading to bowing, warpage, or cracking. On the blade side, heat softens the bond matrix, accelerates wear, and increases the chance of deflection, which can widen kerf and degrade die edge quality.

The degree of sensitivity varies by material. Silicon tolerates moderate thermal stress but suffers yield loss when high temperatures induce subsurface damage. Gallium arsenide (GaAs), lithium niobate (LiNbO₃), indium phosphide (InP), and sapphire are brittle and prone to catastrophic fracture from even small increases in temperature. Silicon carbide (SiC) is extremely hard and generates more frictional heat, which rapidly loads the blade if coolant delivery is insufficient. In all cases, the effects of heat buildup include front-side chipping, backside breakout, microcracking, kerf distortion, and premature blade failure.

Coolant flow is the primary defense against thermal issues. If coolant does not reach the blade–wafer interface, slurry accumulates inside the kerf, trapping heat and raising blade load. This is especially problematic when dicing wafers with narrow scribe streets (20–30 µm), where coolant penetration is restricted. Deionized (DI) water is the industry standard, but additives such as surfactants, lubricants, and anti-static agents such as SMART CUT dicing coolant lower surface tension, improve wetting, and reduce friction. Some advanced processes inject CO₂ into the coolant stream to further reduce static charge and improve thermal stability.

The delivery method and pressure are equally important. Standard flood cooling may be sufficient for wider kerfs and thicker wafers, but high-pressure jet systems or multi-nozzle arrangements are essential for thin wafers, brittle materials, and ultra-narrow kerfs. These systems force coolant deep into the cutting zone, flushing debris and stabilizing temperature throughout the cut. For hard materials like SiC or sapphire, high-pressure delivery is often the difference between stable cutting and immediate blade loading.

Process monitoring helps identify heat buildup before it causes damage. Many dicing saws track spindle load, vibration, or acoustic emission signals, which rise when cutting forces increase due to poor cooling or debris compaction. A rising spindle load curve is often the first indicator of thermal stress. By adjusting feed rate, verifying coolant pressure, or swapping a worn blade, operators can prevent wafer loss.

Thermal effects must be considered during parameter optimization. Higher spindle speeds (30,000–50,000 RPM) spread the cutting load across more diamond particles, reducing heat per contact point, but only if coolant flow is sufficient. Lower feed rates reduce heat generation but risk blade loading if slurry is not flushed. Balancing feed, RPM, bond hardness, and coolant delivery is key to achieving stable thermal conditions across diverse wafer materials.

In advanced semiconductor manufacturing, even small amounts of thermal damage can lead to latent failures. Microcracks formed from local hot spots may not cause immediate wafer breakage but can reduce die strength, causing issues later in assembly or during device operation. For this reason, thermal control is treated as a primary quality parameter, alongside chipping, kerf width, and blade wear, in modern wafer dicing operations.

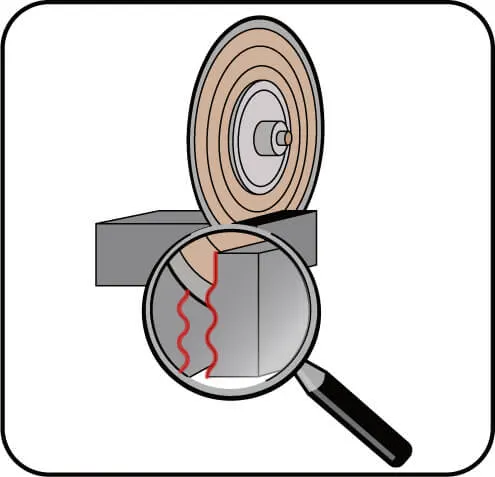

Kerf Width Control

Kerf width control is one of the most critical challenges in wafer dicing because it directly impacts die count, alignment, and packaging yield. As devices scale down and scribe lines become narrower, the tolerance window for kerf accuracy continues to shrink. A kerf that deviates by only 1–2 µm from specification may appear insignificant on a single cut, but across a full wafer containing hundreds or thousands of dies, it can lead to substantial yield loss and misalignment issues during downstream assembly.

Several factors influence kerf stability. Blade wear is a primary cause of kerf widening. As diamonds dull or dislodge, the blade loses its sharpness and requires greater cutting force, which increases lateral deflection. The worn blade also rubs against the wafer sidewalls, enlarging the kerf and introducing subsurface microcracks. Regular dressing is required to maintain blade sharpness, but improper or delayed dressing can accelerate kerf drift.

Vibration and spindle runout are equally important contributors. Even slight vibration from an imbalanced spindle, loose flanges, or excessive blade exposure can cause the blade to wobble during rotation, producing kerf variations along the cut. For blades as thin as 20–30 µm, exposure must be minimized—typically no more than 3–6 times the blade thickness—to maintain stiffness. Flange diameter should be at least one-third of blade diameter, and tightening torque must be controlled precisely to avoid misalignment that can amplify runout.

Material properties also affect kerf control. Harder wafers such as SiC or sapphire generate higher cutting forces, making it more difficult to hold kerf width without deflection. Brittle wafers such as GaAs or InP require extremely narrow kerfs and fine blades, which magnify the impact of even slight instability. Silicon, while more forgiving, still demands tight kerf control in advanced logic and memory devices where scribe lines are extremely narrow.

Process parameters must be tuned to support kerf accuracy. Feed rates that are too aggressive increase side forces, causing blade deflection and kerf widening. Spindle speeds that are too low result in excessive diamond loading per grain, also widening kerf. Conversely, overly high speeds without proper stability can induce vibration. Optimal settings vary by material and blade type, but achieving balance between feed rate, spindle speed, blade thickness, and bond hardness is essential to keeping kerf uniform and minimizing die loss.

Coolant delivery also plays a role in kerf control. Insufficient flushing allows slurry to accumulate inside the cut, creating uneven side pressure on the blade that widens kerf and destabilizes the cut path. High-pressure or multi-jet DI water systems improve kerf consistency by removing debris quickly and stabilizing the cutting zone.

In advanced packaging and high-density device applications, kerf requirements may demand ultra-thin blades as narrow as 20 µm. At this scale, spindle stability, precise alignment, optimized flange design, and constant process monitoring become mandatory. Even a small error in torque, coolant pressure, or exposure ratio can result in kerf variation beyond acceptable limits.